SYSTEMY PDH WYŻSZYCH RZĘDÓW

Hierarchia

systemów PDH.

Opisany w poprzednim rozdziale system PCM 30/32 czy też stosowany w USA system PCM24 umożliwiają zwielokrotnienie i przesyłanie jednym torem 30 (24) kanałów telefonicznych. Przepływności binarne, jakie są w tych systemach generowane wynoszą 2048kbit/s (1544kbit/s). Pasmo wymagane do transmisji tych sygnałów to ok. 1MHz (0.8MHz). Zarówno niewielka liczba kanałów jak i stosunkowo wąskie pasmo implikują stosowanie w systemach teletransmisyjnych urządzeń umożliwiających dalsze zwielokrotnienia. W Europie przyjęto stosowanie następującej hierarchii systemów PDH (zalecenie G.751):

-podstawowy kanał telefoniczny - 64kbit/s,

-system 1 rzędu - 2048kbit/s (PCM 30/32),

-system 2 rzędu ( zwielokrotnienie x 4 ) - 8448kbit/s,

-system 3 rzędu ( zwielokrotnienie x 4 traktów 2 rzędu ) - 34368kbit/s,

-system 4 rzędu ( zwielokrotnienie x 4 traktów 3 rzędu ) - 139264kbit/s,

-system 5 rzędu ( zwielokrotnienie x 4 traktów 4 rzędu ) - 564992kbit/s.

W Polsce pracują systemy do 4 rzędu włącznie .

Amerykańska ( w sieci telefonicznej towarzystw Bella ) hierarchia systemów PDH to:

-podstawowy kanał telefoniczny - 64kbit/s,

-system 1 rzędu - 1544kbit/s (PCM 24),

-system 2 rzędu ( zwielokrotnienie x 4 ) - 6312kbit/s,

-system 3 rzędu ( zwielokrotnienie x 7 traktów 2 rzędu ) - 44736kbit/s,

-system 4 rzędu ( zwielokrotnienie x 6 traktów 3 rzędu ) - 274176kbit/s.

System PCM24 występuje w Polsce w niewielkiej ilości egzemplarzy.Ponadto wyróżnić można także system 2 rzędu (8448kbit/s) z kodowaniem bezpośrednim. Nie są to jednak rozwiązania standardowe.

Zasady tworzenia systemów PDH wyższego rzędu.

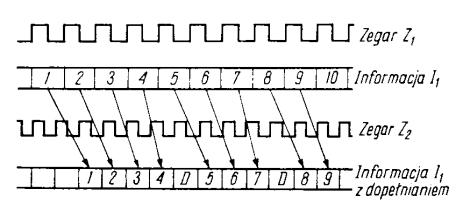

W systemie PCM30/32 w krotnicy następowało jednocześnie kodowanie i zwielokrotnienie. Zwielokrotnienie odbywało się poprzez wstawianie do sygnału zbiorczego kolejno ciągów ośmiu impulsów kodowych z poszczególnych kanałów. Ten sposób zwielokrotnienia nazywany jest przeplotem bajtowym. Jest on bardzo wygodny we współpracy z urządzeniami komutacyjnymi, jednak w urządzeniach, w których należy połączyć w jeden sygnał zbiorczy cztery strumienie binarne sterowane własnymi zegarami stosuje się inną metodę, a mianowicie przeplot bitowy. Zasadę przeplotu bitowego ilustruje poniższy rysunek.

Zasada zwielokrotnienia z przeplotem bitowym.

Strumienie impulsów binarnych o czasie trwania impulsu T są łączone w krotnicy nadawczej w jeden strumień impulsów o czasie trwania , gdzie wypełnienie czasu T, to cztery impulsy z każdego strumienia po jednym. Po stronie odbiorczej następuje proces odwrotny. Aby takie zwielokrotnienie mogło zajść, należy utworzyć ramkę sygnału wyższego rzędu dla celów identyfikacji numerów strumieni po stronie odbiorczej. Ponadto dla takiego układu zwielokrotniającego, jak na rys.3.1, wymagana jest identyczność zegarów wszystkich traktów niższego rzędu. W praktyce jest to niemożliwe do osiągnięcia (dopuszczalna odchyłka przepływności w trakcie 2Mbit/s wynosi bit/s). Można byłoby zatem stosować np. jeden centralny zegar tworząc w ten sposób sieci synchroniczne ograniczone do niewielkiej ilości obiektów, lub w skali krajowej i międzynarodowej zastosować inną metodę umożliwiającą dokonanie zwielokrotnienia, jaką jest tzw. dopełnianie impulsowe.

Dopełnianiem impulsowym nazywa się metodę wyrównywania zmiennej przepływności zwielokrotnianego sygnału cyfrowego do pewnej przepływności odniesienia, którą w tym przypadku jest przepływność grupy wyższego rzędu w przeliczeniu na jeden sygnał cyfrowy niższego rzędu. Wyrównywanie to jest dokonywane na drodze wprowadzenia do sygnału cyfrowego dodatkowych bitów, tzw. bitów dopełniających, lub też wymazywania bitów informacyjnych, przy czym wartość bitów wymazanych przesyłana jest do odbiornika za pomocą bitów znajdujących się w kanale służbowym. Ażeby w odbiorniku można było przywrócić pierwotną postać sygnału cyfrowego, o każdej operacji przeprowadzonej w nadajniku przesyła się informację do odbiornika, w którym przeprowadza się operacje odwrotne. Rozróżnia się trzy rodzaje dopełniania impulsowego:

-dopełnianie dodatnie,

-dopełnianie ujemne,

-dopełnianie dodatnio-ujemne.

Przy dopełnianiu dodatnim zakłada się, iż maksymalne przepływności wszystkich sygnałów wejściowych podlegających zwielokrotnieniu są mniejsze od przepływności, jaka jest przewidziana do transmisji tych sygnałów w sygnale zbiorczym. Sygnały wejściowe przechodzą przez układy synchronizujące, które określają, o ile trzeba zwiększyć ich przepływność, ażeby stały się one synchroniczne z sygnałem grupy wyższego rzędu

Zasada dodatniego dopełniania impulsowego.

Elastyczna pamięć wejściowa, znajdująca się w każdym układzie synchronizującym, pozwala na dopełnienie sygnału wejściowego o pewną liczbę bitów. Informacja o występowaniu bitów dopełniających przekazywana jest do stacji odbiorczej,w której bity te zostaną pominięte, jako zbędne, ponieważ nie niosą one informacji. Sposób realizacji dodatniego dopełniania impulsowego przedstawiony jest poniżej

Sposób

realizacji dodatniego dopełniania impulsowego.

Sposób

realizacji dodatniego dopełniania impulsowego.

W części nadawczej informacja wejściowa wpisywana jest do pamięci w takt sygnału o częstotliwości , odpowiadającej przepływności sygnału wejściowego. Odczyt z pamięci dokonywany jest z częstotliwością , synchroniczną z zegarem krotnicy cyfrowej. Ponieważ częstotliwość jest większa od , układ odczytu ma tendencję do całkowitego opróżniania pamięci. Specjalny układ kontrolny porównuje fazy sygnałów wpisującego i odczytującego, a tym samym stan zajętości pamięci. Kiedy wypełnienie pamięci zmniejsza się poniżej dopuszczalnej granicy, układ kontrolny powstrzymuje jeden impuls sygnału czytającego, dzięki czemu pamięć powraca do stanu zajętości powyżej wartości granicznej, natomiast w sygnale wyjściowym z pamięci jeden bit zostanie powtórzony, czyli zostanie dodany bit, którego nie było w sygnale wejściowym ( bit dopełniający ). W ramce grupy wyższego rzędu określone jest miejsce, w którym może znajdować się bit dopełniający, dlatego do odbiornika wystarczy przesłać informację, że nastąpiło dopełnienie. Po stronie odbiorczej bit dopełniający usuwany jest z sygnału cyfrowego, przez powstrzymanie zapisu do pamięci odbiorczej na czas trwania tego bitu. W ten sposób otrzymuje się sygnał o przepływności binarnej takiej, jaką miał sygnał wejściowy, jednakże z nieciągłościami fazy o amplitudzie jednego bitu. Filtracja fluktuacji fazowych uzyskiwana jest za pomocą pętli ustalania fazy, zawierającej układ porównania fazy, filtr dolnoprzepustowy oraz generator sterowany napięciowo (VCO). Układ porównania fazy porównuje fazę sygnału wpisującego z fazą sygnału otrzymywanego z VCO (sygnał odczytu), dostarczając napięcia proporcjonalnego do różnicy fazy między nimi. Napięcie to, odpowiednio odfiltrowane, steruje generatorem VCO, którego częstotliwość podąża za zmianami częstotliwości sygnału wejściowego w krotnicy nadawczej.

Przy dopełnianiu ujemnym zakłada się, iż częstotliwość zapisu w pamięci nadawczej jest większa od częstotliwości odczytu . W związku z tym wypełnienie pamięci będzie się zwiększać aż do całkowitego jej zapełnienia, jednak zanim to nastąpi kontrolny układ progowy powstrzymuje zapis na czas 1 bitu. Informacja o tym, że nastąpiło opuszczenie (wymazanie) bitu oraz wartość tego bitu przesyłane są do odbiornika w kanale służbowym. Urządzenie odbiorcze wydziela tę informację, powstrzymuje odczyt z pamięci odbiorczej na czas 1 bitu, a zarazem do sygnału wyjściowego dodaje w tym czasie bit, który został opuszczony w nadajniku. Pozwala to na transmisję sygnału bez straty informacji, jednak przepływność zbiorczego sygnału zwielokrotnionego jest większa niż suma przepływności sygnałów zwielokrotnianych. Ażeby określić niezbędne zwiększenie przepływności sygnału zbiorczego konieczne jest zaznajomienie się ze strukturą ramki, składającej się z następujących elementów:

- bitów informacyjnych służących do przesłania zwielokrotnianych cyfrowo sygnałów wejściowych z przeplataniem bitów,

- sygnału fazowania ramki, który pozwala na właściwy rozdział bitów do poszczególnych kanałów informacyjnych,

- bitów dopełniających,

- bitów kontroli dopełniania,

- bitów służących dla celów służbowych, przeznaczonych np. do przesyłania alarmów do stacji współpracującej.

Zespół powyższych bitów tworzy ramkę systemu zwielokrotnienia cyfrowego. W przeprowadzanej analizie wymaganego zwiększenia przepływności sygnału zbiorczego wprowadzimy następujące oznaczenia:

- przepływność binarna grupy wyższego rzędu,

- przepływność binarna grupy niższego rzędu,

N - liczba zwielokrotnianych grup niższego rzędu,

- przepływność binarna kanału przewidzianego do transmisji jednej grupy niższego rzędu w sygnale zbiorczym,

P - liczba bitów nadmiarowych w ramce, składających się z:

- bitów sygnału fazowania ramki,

- bitów służbowych,

- bitów kontroli dopełniania,

Q - liczba bitów informacyjnych w ramce (łącznie z bitami dopełniającymi).

Dla dowolnego rodzaju zwielokrotnienia cyfrowego przepływność binarną sygnału zwielokrotnionego (zbiorczego) można wyrazić następującą zależnością:

Przy dopełnianiu dodatnim zakłada się, że:

czyli,korzystając

Zakładając, że:

i podstawiając do otrzymujemy:

(k)

Człon (1+a) we wzorze (k) reprezentuje wzrost przepływności sygnału wyższego rzędu w stosunku do sumy przepływności sygnałów niższego rzędu, wynikający z dopełniania. Wzrost ten jest bardzo mały w porównaniu ze wzrostem wynikającym z dodania bitów dla potrzeb fazowania ramki, kontroli dopełniania i celów służbowych - człon (1+P/Q). Częstotliwość dopełniania można określić jako różnicę częstotliwości i . Przy nominalnych częstotliwościach F i f , częstotliwość dopełniania wynosi więc:

Omówiony powyżej proces dopełniania impulsowego wymaga stosowania na wejściu krotnicy cyfrowej specjalnej pamięci elastycznej dla każdego sygnału zwielokrotnianego. Stosowanie pamięci do magazynowania bitów informacyjnych sygnałów wejściowych niezbędne jest również ze względu na konieczność wprowadzenia do ramki sygnału zbiorczego dodatkowych bitów sygnału fazowania ramki, bitów służbowych i bitów kontroli dopełniania. Pojemność pamięci musi być tak dobrana, ażeby mogła absorbować największe zmiany fazy, obejmujące zarówno wprowadzania sygnału fazowania ramki, jak i fluktuacje fazy w sygnale wejściowym powodowane przez trakt liniowy.

W większości urządzeń asynchronicznego zwielokrotnienia cyfrowego pamięć elastyczna ma pojemność 8 bitów o następującym przeznaczeniu:

- trzy bity przeznaczone są na wytworzenie szczelin służących do wprowadzania sygnału fazowania ramki, a wśród nich zawarte są przerwy potrzebne do wprowadzenia rozkazów o dopełnianiu,

- jeden bit wynika z czasu oczekiwania, ponieważ z założenia dopełnianie nie może być natychmiast realizowane,

- pół bitu przeznacza się na niedokładność pracy urządzeń,

- trzy i pół bitu przeznacza się na ewentualne fluktuacje fazowe występujące w sygnale wejściowym oraz niestałość przepływności binarnej sygnału oraz niestałość częstotliwości generatora VCO.

Układy złożone z pamięci elastycznej, komparatora fazy, bloku sterowania odczytem pamięci i dopełnianiem w części nadawczej krotnicy, oraz układy pamięci, komparatora, detektora dopełniania i sterowania zapisem pamięci w części odbiorczej, stanowią wyposażenie każdego z czterech traktów niższego rzędu. Metoda zwielokrotnienia w całej hierarchii systemów PDH jest identyczna. W zależności od rzędu systemu zmieniają się tylko szybkości elementów półprzewodnikowych, wymagania na stabilność urządzeń i struktura ramki sygnału. Spełniany jest jednocześnie warunek, że stosowanie zwielokrotnienia wyższego rzędu nie wpływa w żaden sposób na sygnały niższych rzędów.

WŁAŚCIWOŚCI I

ARCHITEKTURA SYSTEMÓW CYFROWYCH.

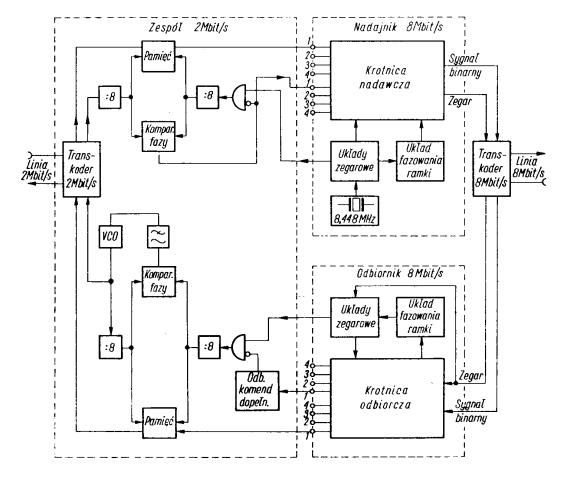

Hierarchia plezjochronicznych systemów cyfrowych PCM odzwierciedla jednocześnie metodę tworzenia strumieni o większych przepływnościach. Otóż, aby otrzymać sygnał zbiorczy o np. przepływności 140Mb/s (1920 kanałów telefonicznych) należy przeprowadzić trzy etapy zwielokrotnienia 2/8Mbit/s, 8/34Mbit/s i wreszcie 34/140Mbit/s. Sygnał pojedynczego kanału telefonicznego musi zatem przejść przez krotnicę 2Mbit/s i trzy w/w krotnice po stronie nadawczej i w odwrotnej kolejności dla odbiorczej części systemu. Zwielokrotnienie 2Mbit/s zostało opisane. Pozostałe "obiekty" zwane systemami zwielokrotnienia wyglądają następująco:

System 8Mbit/s.

System zwielokrotnienia cyfrowego o przepływności 8448kbit/s przeznaczony jest do zwielokrotnienia czterech plezjochronicznych sygnałów cyfrowych o nominalnej przepływności 2048kbit/s. Struktura ramki tego systemu przedstawiona jest na rys.4.1.

|

GRUPA |

NUMERY BITÓW W GRUPIE |

|||||||||||||||||

|

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9

|

10 |

11 |

12 |

13 |

14 |

15 |

... |

211 |

212 |

|

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

AL |

NU |

T1 |

T2 |

T3 |

... |

T3 |

T4 |

|

2 |

C1 |

C2 |

C3 |

C4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

... |

T3 |

T4 |

|

3 |

C1 |

C2 |

C3 |

C4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

... |

T3 |

T4 |

|

4 |

C1 |

C2 |

C3 |

C4 |

D1 |

D2 |

D3 |

D4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

... |

T3 |

T4 |

Struktura sygnału (ramki) systemu 8Mbit/s.

Ramka składa się z 4 grup, z których każda zawiera 212 bitów. W ramce, składającej się z 848 bitów, 24 bity przeznacza się do celów fazowania ramki, dopełniania i sterowania procesem dopełniania. Do przesyłania informacji z grup pierwotnych przeznacza się 824 bity, to znaczy po 206 dla każdej z grup. Odpowiada to przepływności binarnej 2052,2kbit/s, czyli większej od 2048kbit/s z maksymalną dodatnią odchyłką. Ażeby w dłuższym czasie przesyłać średnio 2048kbit/s, należy w ramce grupy wtórnej przesyłać na przemian 206 bitów lub 205 bitów. Jeżeli przesyła się 205 bitów, wówczas jeden z 206 bitów będący do dyspozycji nie jest wykorzystany, zachodzi wówczas proces dopełniania.Rolę bitów dopełniających pełnią bity w grupie IV. Informacja o tym, czy dopełnianie zachodzi czy nie, przesyłana jest za pomocą bitów Cij. Jeżeli dopełnianie zachodzi, wówczas przesyłana jest kombinacja 111, natomiast gdy dopełniania nie ma - kombinacja 000. Częstotliwość dopełniania zależna jest od przepływności grupy wtórnej i przepływności grupy pierwotnej. Dla ich nominalnych wartości przepływność dopełniania wynosi:

)

Przy zmianach przepływności grupy pierwotnej o bit/s i przepływności grupy wtórnej o bit/s proces dopełniania zachodzi ze zmienną częstotliwością, dzięki czemu zapewniona jest poprawna transmisja grupy pierwotnej.

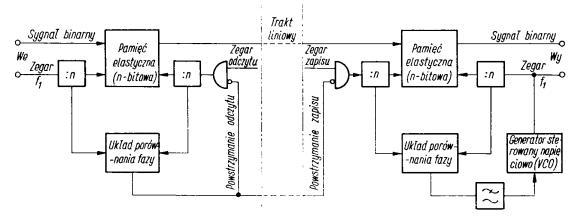

Schemat blokowy krotnicy systemu PDH

Schemat blokowy krotnicy systemu zwielokrotnienia cyfrowego o przepływności

8448kbit/s z dopełnieniem dodatnim.

Wejściowa część krotnicy wyposażona jest w 4 zespoły 2Mbit/s. W skład każdego zespołu wchodzą: transkoder 2Mbit/s, zespół pamięci wejściowej oraz zespół pamięci wyjściowej. W transkoderze sygnał cyfrowy przychodzący z linii jest dekodowany z kodu liniowego na kod binarny oraz wyławiany jest sygnał taktowania 2.048MHz. Sygnał binarny oraz sygnał taktowania podawane są do zespołu pamięci wejściowej, w którym dokonywana jest operacja dopełniania. Sygnał wyjściowy z zespołu pamięci wejściowej (synchroniczny z częstotliwością grupy wtórnej) podawany jest do nadajnika 8Mbit/s, w którym następuje zwielokrotnienie cyfrowe oraz wprowadzenie do sygnału zbiorczego bitów dodatkowych, tzn. sygnału fazowania ramki, komend dopełniania i bitów służbowych. W nadajniku 8Mbit/s generowany jest poza tym sygnał taktowania 8,448MHz oraz wszystkie przebiegi zegarowe potrzebne do sterowania pamięci wejściowych. Wyjściowy sygnał binarny 8,448Mbit/s oraz sygnał taktowania podawany jest do transkodera 8Mbit/s, który zamienia sygnał binarny na sygnał liniowy.

Po stronie odbiorczej krotnicy wykonywane są operacje odwrotne. Sygnał przychodzący z linii jest regenerowany i dekodowany z kodu liniowego na kod binarny. Sygnał binarny wraz z odtworzonym sygnałem taktowania 8,448MHz podawany jest do odbiornika 8Mbit/s. Układ odbiornika 8Mbit/s zapewnia fazowanie ramki urządzenia odbiorczego, generację wszystkich przebiegów zegarowych potrzebnych do sterowania pamięci wyjściowych oraz rozdział sygnału na 4 ciągi cyfrowe odpowiadające poszczególnym grupom pierwotnym 2,048Mbit/s. W zespole pamięci wyjściowej, po usunięciu bitów dopełniających, odtwarzany jest pierwotny sygnał binarny 2,048Mbit/s oraz sygnał taktowania 2,048MHz. Sygnał ten podawany jest następnie do transkodera 2Mbit/s, w którym zostaje zakodowany na kod liniowy i wysłany w linię.

System 34Mbit/s..

System zwielokrotnienia cyfrowego o przepływności 34368kbit/s

przeznaczony jest do zwielokrotnienia 4 plezjochronicznych

sygnałów grupy wtórnej o przepływności 8448kbit/s. Struktura ramki

|

GRUPA |

NUMERY BITÓW W GRUPIE |

||||||||||||||||||

|

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9

|

10 |

11 |

12 |

13 |

14 |

15 |

16 |

... |

384 |

|

|

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

AL |

NU |

T1 |

T2 |

T3 |

T4 |

... |

T4 |

|

|

2 |

C1 |

C2 |

C3 |

C4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

T4 |

... |

T4 |

|

|

3 |

C1 |

C2 |

C3 |

C4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

T4 |

... |

T4 |

|

|

4 |

C1 |

C2 |

C3 |

C4 |

D1 |

D2 |

D3 |

D4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

T4 |

... |

T4 |

|

Struktura ramki systemu zwielokrotnienia cyfrowego o przepływności 34368kbit/s.

Ramka grupy trójnej składa się z 4 grup po 384 bity każda. Sygnał kontroli dopełniania jest rozłożony w ramce podobnie jak w ramce systemu 2 rzędu a jego postać jest identyczna, podobnie jak sygnału fazowania ramki i bitów służbowych. Schemat blokowy, jak również zasada działania krotnicy jest analogiczna jak w przypadku krotnicy 2 rzędu (8Mbit/s).

System 140Mbit/s.

System zwielokrotnienia cyfrowego o przepływności 139,264Mbit/s przeznaczony jest do zwielokrotnienia cyfrowego 4 grup trójnych o przepływności 34,368Mbit/s każda.Zasada działania systemu jest podobna jak krotnic rzędu 2 i 3.

Struktura ramki grupy czwórnej j

|

GRUPA |

NUMERY BITÓW W GRUPIE |

||||||||||||||||||

|

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

... |

488 |

|

|

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

AL |

NU |

NU |

NU |

... |

T4 |

|

|

2 |

C1 |

C2 |

C3 |

C4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

T4 |

... |

T4 |

|

|

3 |

C1 |

C2 |

C3 |

C4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

T4 |

... |

T4 |

|

|

4 |

C1 |

C2 |

C3 |

C4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

T4 |

... |

T4 |

|

|

5 |

C1 |

C2 |

C3 |

C4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

T4 |

... |

T4 |

|

|

6 |

C1 |

C2 |

C3 |

C4 |

D1 |

D2 |

D3 |

D4 |

T1 |

T2 |

T3 |

T4 |

T1 |

T2 |

T3 |

T4 |

... |

T4 |

|

Struktura

ramki systemu zwielokrotnienia cyfrowego o przepływności 139,264Mbit/s.

Ramka składa się z 6 grup po 488 bitów każda. Sygnał fazowania ramki składa się z 12 bitów (111110100000) umieszczonych na początku grupy 1. Do celów kontroli dopełniania przewidziane są sekwencje pięciobitowe, które dają zabezpieczenie przed dwoma przekłamaniami. Do celów służbowych przeznaczone są cztery bity.