ZESPÓŁ

SYNCHRONIZUJĄCY GSS

v WIADOMOŚCI

OGÓLNE

Zespół składa się z czterech

jednakowych modułów MSS0

÷MSS3, sterowanych z procesora ELS. Każdy z modułów

połączony jest z koncentratorem oddalonym dwoma traktami PCM, z centrum

komutacyjnym zaś – dwiema grupami torów LR. Zadania zespołu

synchronizacji są następujące:

a) synchronizacja

pobieranych kanałów rozmównych,

b) dekodowanie

informacji sygnalizacyjnych i meldunków z wieloramki sygnalizacyjnej oraz

przesłanie ich do centrum komutacyjnego,

c) organizacja

wieloramki sygnalizacyjnej w kierunku do koncentratora.

Schemat blokowy zespołu został

przedstawiony w następujący sposób:

UKŁAD

BLOKOWY ZESPOŁU GSS

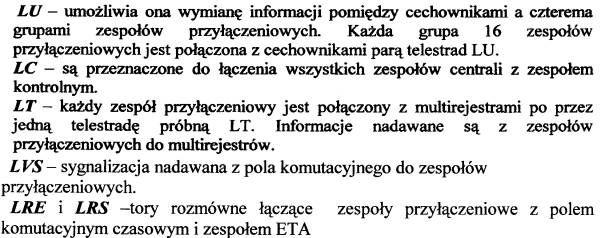

ü SCHEMAT IDEOWY MODUŁU

MSS ZESPOŁU GSS

W skład jednego modułu wchodzą następujące

układy :

a)

układ CRM

synchronizacji odbieranych kanałów PCM,

b)

układ wymiany

informacji systemem kanał w kanał,

c)

układ wymiany

meldunków systemem semafor.

Schemat

ideowy jednego modułu MSS zespołu GSS przedstawiono w następujący

sposób:

SCHEMAT IDEOWY MODUŁU MSS

v

SYNCHRONIZACJA

ODBIERANYCH SYGNAŁÓW KANAŁÓW

PCM

Ciągi impulsów

zegarowych koncentratora odległego różnią się w fazie i częstotliwości od

analogicznych ciągów centrum komutacyjnego,w którym znajduje się zespół

synchronizacji GSS. Synchronizacja odbieranych sygnałów polega na

kompensacji tych różnic w złożonych granicach. Dokonuje się tego, kontrolując

zapis za pomocą wybranego taktu spośród ciągów impulsowych

ω0÷ω7.

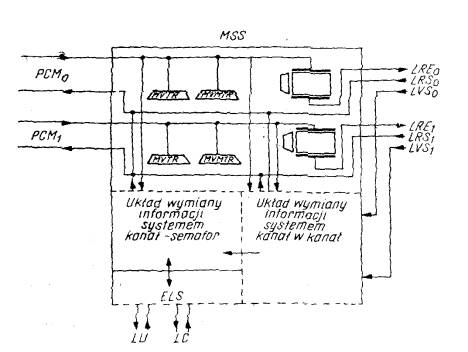

ü SCHEMAT

LOGICZNY ZESPOŁU

SYNCHRONIZACJI KANAŁÓW ROZMÓWNYCH

Każdy kanał VTi odbierany traktem PCM

wpisywany jest do rejestru R1 w rytmie zegara koncentratora

odległego HD. Tak więc informacja kanału VTi znajdzie

się w rejestrze R1 w chwili ti+1, w rejestrze zaś R2

– w chwili ti+1 .Schemat logiczny przedstawiony jest w następujący

sposób:

SCHEMAT LOG. ZESPOŁU SYNCH. KANAŁÓW ROZM.

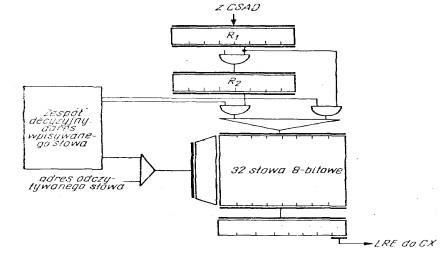

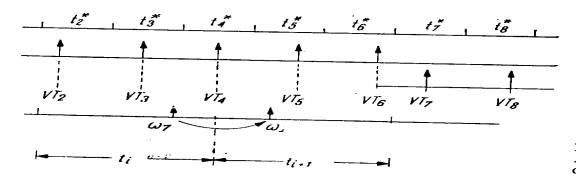

Na poniższym rysunku ukazane są

zależności czasowe dla przypadku, gdy zegar centrum komutacyjnego [ HL ], jest

opóźniony w stosunku do HD. Kanał VT7 nie zostanie

wpisany do pamięci, a więc zostanie stracony.

UKŁAD KANAŁÓW HL < HD

W sytuacji przedstawionej na powyższym

rysunku, aby zapobiec stracie VTi należy dokonać zapisu nieco

wcześniej, co zostało zilustrowane schematycznie na poniższym rysunku:

ADRES ZAPISU

DLA HL < HD

Decyzję taką podejmuje układ decyzyjny

adresu zapisu, kontrolujący wzajemne przesuwanie się zegarów HL i HD. W

zobrazowanym przykładzie układ decyduje o dokonywaniu zapisu w chwili

wyznaczonej impulsem ω3, zamiast w chwili ω7.

POWRÓT